纵横 2.5D

奇峰之间,道路纵横交错。策略之间,智谋纷繁交织。

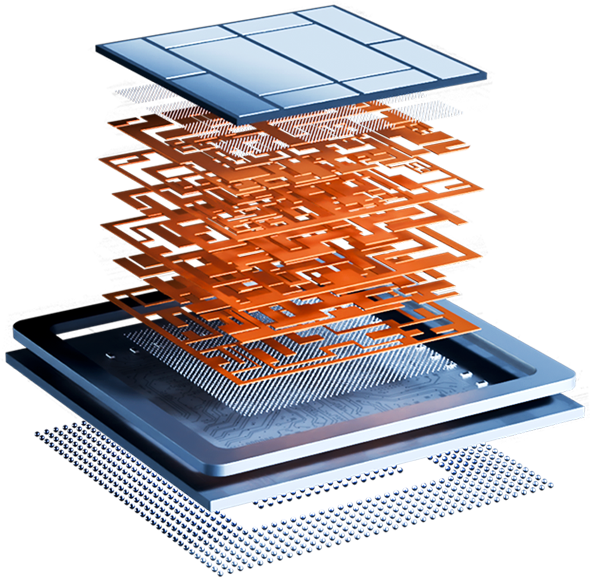

好比于通过复杂交错之布线层,在“横”向广度上跨越不同界限,在“纵”向高度上达到新的层次,实现多个芯片2.5D高密度互连。

完成跨领域的整合与统一。

2.5D封装解决方案

通过TSV、TMV、RDL、uBump、Chip to Wafer、Wafer molding等工艺技术,以Si基、有机RDL或混合RDL等Interposer上集成多颗芯片的方式,实现产品高互连密度、高带宽、高速和小尺寸的集成,缩短产品设计周期和降低设计难度。

奇峰之间,道路纵横交错。策略之间,智谋纷繁交织。

好比于通过复杂交错之布线层,在“横”向广度上跨越不同界限,在“纵”向高度上达到新的层次,实现多个芯片2.5D高密度互连。

完成跨领域的整合与统一。

通过TSV、TMV、RDL、uBump、Chip to Wafer、Wafer molding等工艺技术,以Si基、有机RDL或混合RDL等Interposer上集成多颗芯片的方式,实现产品高互连密度、高带宽、高速和小尺寸的集成,缩短产品设计周期和降低设计难度。